РАДИОТЕХНИКА И ЭЛЕКТРОНИКА, 2006. том 51, № I, с. 125-128

НОВЫЕ РАДИОЭЛЕКТРОННЫЕ СИСТЕМЫ И ЭЛЕМЕНТЫ

УДК 621.382

ПРОЕКТИРОВАНИЕ ЭЛЕМЕНТОВ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ ДЛЯ ВЫСОКОЧАСТОТНЫХ КОМПЛИМЕНТАРНЫХ МИКРОСХЕМ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ

© 2006 г. В. А. Гергель, Н. М. Горшкова, Я. С. Губин, О. А. Сомов

Институт радиотехники и электроники Российской Академии Наук Поступила в редакцию 20.08.2005 г.

Предложена новая электрическая схема и физическая структура элемента защиты от ЭСР. которая обладает вдвое меньшим сопротивлением для тока ЭСР. Уменьшение сопротивления достигнуто введением дополнительных транзисторов, реализующих функцию обратной связи. Применение новой схемы элемента защиты и новой методики моделирования с учетом подложечных транзисторов позволило уменьшить площадь элемента в 1.5 раза, а его электрическую емкость в 1.6 раза.

Развитие современной технологии полупроводниковых микросхем и микроэлектронных устройств идет не только по пути уменьшения размеров полупроводниковых элементов на кристаллах, но и в направлении уменьшения размеров корпусов больших интегральных схем (БИС) и элементов на печатной плате.

Со времени создания первых БИС паразитные емкости в сигнальных цепях на плате удалось уменьшить более чем в 10 раз, а рабочие частоты устройств значительно возросли. Входные и выходные емкости полупроводниковых элементов стали сравнимы с емкостями корпусов и печатных плат. Емкости входных и выходных цепей современных БИС почти полностью определяются емкостями элементов защиты от электростатических разрядов (ЭЗЭСР). Повышение рабочих частот современных БИС требует уменьшения емкостей сигнальных цепей за счет снижения паразитных емкостей ЭЗЭСР.

Электростатические разряды (ЭСР) воздействуют на микросхемы как в процессе их производства, так и в процессе их монтажа на платы и эксплуатации [1]. Причем в процессе эксплуатации воздействию ЭСР подвержены только те выводы, которые подключены к внешним разъемам устройства и предназначены для организации внешних связей. Источниками разрядов могут быть люди - операторы технологических процессов, механизмы для обработки изделий и кабели линий связи. Для этих случаев разработаны модели источников ЭСР. Однако методы защиты для всех видов источников общие.

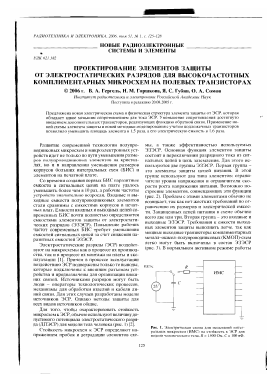

Для того, чтобы охарактеризовать стойкость микросхем к ЭСР, обычно используют величину допустимого потенциала электростатического разряда (ДПЭСР) для модели тела человека (рис. 1) [2].

Стойкость микросхем к ЭСР определяют напряжением пробоя и деградации элементов схе-

мы, а также эффективностью используемых ЭЗЭСР. Основная функция элементов защиты состоит в переключении разрядного тока из сигнальных цепей в цепь заземления. Для этого используются две группы ЭЗЭСР. Первая группа -это элементы защиты цепей питания. В этой группе используют два типа элементов: ограничители уровня напряжения и ограничители скорости роста напряжения питания. Возможно построение элементов, совмещающих эти функции (рис. 2). Проблем с этими элементами обычно не возникает, так как нет жестких требований по ограничению их размеров и электрической емкости. Защищенных цепей питания в схеме обычно всего две или три. Вторая группа - это входные и выходные ЭЗЭСР. Требования к емкости выходных элементов защиты выполнить легче, так как мощные выходные транзисторы комплиментарных металл-окисел-полупроводниковых (КМОП)-схем легко могут быть включены в состав ЭЗЭСР (рис. 3). В нормальном активном режиме работы

П.';'? С

Рис. 1. Электрическая схема для испытаний интегральных микросхем (ИМСЛ на стойкость к ЭСР для модели человеческого тела, Я = 1500 Ом, С = 100 пФ.

¿>1

02

±~ не"

м.

гРМ/

ЧЁ^

О

и

ЧБ?

М,

ип

м.

Рис. 2. Элемент защиты цепей питания.

Вход 1

Вход 2

ЭЗЭСР

Выходной каскад

имс

Рис. 3. Защита выходных каскадов интегральных микросхем (ИМС) от ЭСР.

выходных каскадов емкости мощных транзисторов не являются паразитными и связаны с функционированием устройства.

Задачей входных элементов защиты является ограничение напряжения на затворах входных КМОП-элементов, которая реализуется переключением входного тока ЭСР в цепи питания.

Наиболее опасные режимы ЭСР возникают при втекающем разрядном токе и заземленной общей шине. В этих режимах полярность напряжения на шинах питания соответствует нормальному активному режиму работы схемы, а ток через функциональные элементы КМОП-схемы очень мал. В других режимах напряжение в шинах питания инвертируется, и открываются изолирующие р-п - переходы в структуре БИС. Ток может протекать не только через элементы защиты, но и через функциональные элементы схемы, а общее сопротивление в цепи разрядного тока уменьшается.

Традиционная методика моделирования элементов защиты от ЭСР включает в себя этап подготовки эквивалентной трактовой схемы и этап расчета и анализа результатов. Причем в эквивалентную трактовую схему включаются только ЭЗЭСР, цепи питания, входные и выходные каскады. Расчет ведут для наихудшего случая и без учета влияния функциональных элементов схемы. паразитных элементов физической структуры и компонентов на монтажной плате. Расчет разрядных токов может быть выполнен в статическом режиме без учета процессов заряда - разряда конденсаторов. На основе такого моделирования разрабатывают конструкцию ЭЗЭСР, которая обеспечивает надежную защиту микросхем с некоторым запасом при заданной величине ДПЭСР.

В тех случаях, когда необходимо предельно уменьшить входную емкость микросхемы, требуется более детальная модель и более эффективная конструкция элементов защиты от ЭСР [3,4].

В данной работе предложена новая методика проектирования ЭЗЭСР, включающая:

1) правила подготовки эквивалентной трактовой схемы для моделирования режимов ЭСР;

2) режимы моделирования ЭСР:

3) схему модифицированного элемента защиты;

4) модель ЭЗЭСР для нормального активного режима работы микросхемы.

Емкости в цепях питания включают конструктивные блокировочные конденсаторы (10... 100 пФ) и эквивалентные емкости функциональных элементов (100...200 пФ на 1 мм2 активной площади кристалла). Емкости функциональных элементов учитываются путем введения в трактовую схему соответствующего эквивалента.

Для интерфейсных выводов микросхем ДПЭСР обычно устанавливают вдвое большим, чем для других сигнальных выводов, так как интерфейсные выводы подвержены действию ЭСР в процессе эксплуатации в составе электронной аппаратуры. В подобном случае испытание этих выводов на стойкость к ЭСР проводят также в составе аппаратуры. Микросхема уже соединена с другими компонентами на печатной плате, а в цепях питания присутствуют внешние блокировочные конденсаторы большой емкости (10... 100 мкФ).

Моделирование режима ЭСР с новой трактовой схемой позволяет прогнозировать увеличение величины ДПЭСР без изменения элементов защиты за счет появления дополнительных путей протекания разрядного тока.

ПРОЕКТИРОВАНИЕ ЭЛЕМЕНТОВ ЗАЩИТЫ

127

Паразитные элементы структуры

Входной каскад

ЭЗЭСР

Рис. 4. Новый элемент защиты от ЭСР.

Моделирование электростатического разряда через выводы микросхемы необходимо выполнять в режиме расчета переходного процесса. Разрядный источник представлен импульсом напряжения в несколько тысяч вольт с фронтами менее 5 не. Критические напряжения возникают в цепях питания и на затворах входных и выходных металл—окисел-полупроводниковых (МОП)-тран-зисторов. Для каждого вывода выполняют расчеты четырех режимов разряда: для втекающего и вытекающего разрядного тока, а также для заземления общей шины или шины питания. Максимальные напряжения в критических точках схемы, рассчитанные в импульсном режиме, значительно меньше величин, полученных при расчетах в статическом режиме.

Основным недостатком простого двухтранзис-торного элемента защиты (рис. 3) является то, что в момент возникновения ЭСР открывается только один из транзисторов. Авторами предложен новый четырехтранзисторный элемент защиты, у которого в момент возникновения ЭСР всегда открываются два мощных транзистора, а сопротивление в цепи разрядного тока уменьшается вдвое (рис. 4). При заданных величинах разрядного напряжения и напряжений в критических точках схемы новый элемент защиты позволяет уменьшить размеры мощных транзисторов вдвое, а электрическую емкость ЭЗЭСР в 1.6... 1.8 раза.

Во многих схемотехнических расчетах ЭЗЭСР представлены только как паразитные емкости. Однако на высоких рабочих частотах проявляют себя и резистивные свойства выключенных МОП-

и„

Вход

о

я,

1 1 П

1 = с, = С2 Ц

1

1 1 2

Выход

1

Рис. 5. Эквивалентная схема входной цепи ИМС с учетом элементов конструкции корпуса (/), ЭЗЭСР (2) и входного каскада (3).

транзисторов. В расчетах элементов согласования рмпедансов для линии связи и приемника (или передатчика) высокочастотных сигналов авторами использована резистивно емкостная последовательная эквивалентная схема замещения ЭЗЭСР (рис. 5). Параметры эквивалентной схемы получены при моделировании входной цепи с использованием радиотехнического симулятора "Microwave office" .

В субмикронных КМОП-технологиях правила проектирования требуют, чтобы с внешними выводами соединялись транзисторы с рабочим напряжением до 3.3В и выдерживающие кратковременную перегрузку до 7В. Такие транзисторы имеют длину затвора не менее 0.45 мкм вне зависимости от размеров элементов во внутренней части схемы. Поэтому для элементов защиты всегда используют транзисторы с длиной затвора не менее 0.45 мкм.

Типовые требования к стойкости входов и выходов микросхем определяют допустимый потенциал электростатического разряда 2000В. Разработаны чертежи топологии типового и модифицированного элементов защиты. Площадь типового элемента защиты составила 1600 мкм2, а модифи-

цированного - 990 мкм2. Электрическую емкость ЭЗЭСР удалось уменьшить от 0.16 пФ до 0,1 пФ.

Использование нового маршрута проектирования элементов защиты от электростатических зарядов позволяет точнее прогнозировать допустимое напряжение разряда, уменьшить входные и выходные емкости микросхемы, лучше согласовать импедансы линий связи и приемников или передатчиков высо

Для дальнейшего прочтения статьи необходимо приобрести полный текст. Статьи высылаются в формате PDF на указанную при оплате почту. Время доставки составляет менее 10 минут. Стоимость одной статьи — 150 рублей.