НАНОЭЛЕКТРОНИКА

УДК 621.3.049.771.14.

ЭЛЕМЕНТНАЯ БАЗА НАНОКОМПЬЮТЕРОВ НА ОСНОВЕ СВЯЗАННЫХ КВАНТОВЫХ ОБЛАСТЕЙ

© 2005 г. Б.Г. Коноплев1-2, Е.А. Рмндин2

Предложены принципы построения наноразмерных логических элементов и элементов памяти сверхскоростных СБИС на основе туннельносвязанных квантовых ям, позволяющие преодолеть ограничения, связанные с временем пролета электронами каналов транзисторов. Обсуждаются результаты моделирования наноразмерных интегральных логических элементов, проблемы и перспективы их использования для построения высокопроизводительных вычислительных систем.

ВВЕДЕНИЕ

Уменьшение размеров интегральных элементов и повышение степени интеграции СБИС - основная тенденция развития микро- и наноэлек-троники.

Современные технологические процессы электронно-лучевой литографии и молекулярно-луче-вой эпитаксии обеспечивают формирование полупроводниковых структур с нанометровыми размерами, что позволяет не только повысить быстродействие и снизить энергию переключения интегральных элементов, но и использовать квантовые эффекты при построении элементной базы вычислительных систем.

С развитием наноразмерной элементной базы, применительно к вычислительным системам, на ее основе стали все чаще использовать термин "нанокомпьютеры".

В настоящее время развитие нанокомпьюте-ров идет по нескольким направлениям, которые можно обобщить в два основных: вычислительные системы с традиционными архитектурами на основе элементной базы на квантовых эффектах с одной стороны, и квантовые компьютеры - с другой.

Разработка и совершенствование элементной базы нанокомьютеров с традиционной архитектурой позволит уже на данном этапе значительно увеличить степень интеграции, быстродействие, вычислительную мощность, снизить энергопотребление вычислительных систем.

1 Таганрогский государственный радиотехнический университет

2 Южный научный центр РАН

ПРИНЦИПЫ ПОСТРОЕНИЯ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ НА ОСНОВЕ ТУННЕЛЬНОСВЯЗАННЫХ КВАНТОВЫХ ЯМ

Создание элементной базы на квантовых ямах, образованных гетеропереходами, является одним из основных направлений развития наноэлектро-ники, в рамках которого разработан ряд полупроводниковых наноструктур с уникальными характеристиками, в частности, транзисторы с модуляцией скорости носителей (velocity modulation transistor - VMT), быстродействие которых не ограничено временем пролета электронами канала [1,2].

VMT-транзисторы имеют два параллельных канала, представляющих собой квантовые ямы, соединяющие области стока и истока и разделенные туннельным гетеропереходным барьером. В первом канале подвижность электронов высокая, а во втором - низкая. Снижение подвижности носителей заряда во втором канале достигается либо посредством легирования области квантовой ямы и рассеяния носителей на ионах примеси [1], либо за счет интенсивного рассеяния на гетеро-границах [2]. В последнем случае ширина второй квантовой ямы значительно меньше ширины первой.

Управление VMT-транзистором осуществляется поперечным электрическим полем, создаваемым двумя вертикально расположенными затворами [1], либо затвором и истоком [2]. Управляющее поперечное поле перераспределяет носители заряда между каналами. При этом открытому состоянию транзистора соответствует перенос основной части электронов в первый канал, где они приобретают высокую скорость дрейфа. Закрытому состоянию соответствует перенос электронов во второй канал, где их подвижность снижает-

-О у[к,

о—

.и

и от

НО СМ

^оит

I

а

-О

^N1

о-

^N2

О-

■с

-о У,

<1с1

ц

^'оит -О

¿-■-■■'---Ек-

1 I

X

-О

1%2 -О

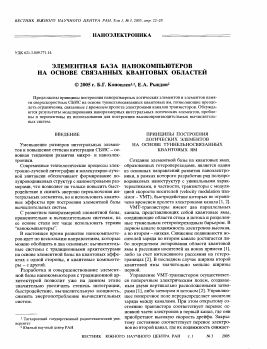

Рис. 1. Схемы логических элементов на основе туннельнос-вязанных квантовых ям: а) инвертор; б) элемент И-НЕ/ИЛИ-НЕ (иш — входное напряжение; иощ- — выходное напряжение)

ся, а сопротивление канала соответственно увеличивается. Таким образом, за время пролета электроны могут несколько раз перераспределяться между двумя параллельными туннельносвязанны-ми каналами, что в принципе позволяет, учитывая крайне малую инерционность процесса туннели-рования, достичь времени переключения значительно меньшего, чем время пролета. При этом суммарное число носителей в каналах должно оставаться практически неизменным [1].

Основным недостатком УМТ-транзисторов является сравнительно низкое отношение токов транзистора в открытом и закрытом состояниях (2-2,5 при температуре Т = 300 К) [1], обусловленное низким отношением значений подвижности носителей в каналах и влиянием эффекта насыщения скорости дрейфа в короткоканальных приборах, что затрудняет использование УМТ для создания интегральных логических элементов [1].

С целью устранения данного недостатка и использования в логических элементах принципов повышения быстродействия, реализованных в УМТ, а также уменьшения площади элементов, снижения потребляемой мощности и энергии переключения авторами разработаны наноразмер-ные интегральные логические элементы на основе туннельносвязанных квантовых ям, принципы построения которых поясняют электрические схемы инвертора и двухвходового вентиля 2И-НЕ/2ИЛИ-НЕ, приведенные на рисунке 1.

Рис. 2. Зонные диаграммы ТСН с электронной проводимостью при различных направлениях управляющего поля (пунктирной линией показан уровень Ферми)

Построение элементов осуществляется в соответствии с принципами комплементарной логики, т.е. на основе пар транзисторов с взаимодополняющими типами проводимости, что обеспечивает резкое снижение потребляемой мощности и повышение помехоустойчивости элементов. С целью повышения быстродействия и преодоления ограничения, связанного с временем пролета подвижными носителями каналов, транзисторы каждого типа проводимости попарно объединяются в туннельносвязанные наноструктуры (ТСН), обозначенные на схемах пунктирными линиями со стрелками (рис. 1).

Зонные диаграммы туннельносвязанной наноструктуры с электронной проводимостью при различных управляющих напряжениях приведены на рисунке 2. Каждая ТСН содержит две нелегированные (в отличие от УМТ [1, 2]) квантовые ямы, разделенные туннельным потенциальным барьером, и два управляющих перехода. В зависи-

О 9

Я

О РШо шв О РШ! О

Рис. 3. Схема элемента статической памяти на основе тун-нельносвязанных квантовых ям

мости от направления поперечного поля управляющих переходов подвижные носители заряда в результате туннелирования концентрируются либо преимущественно в первой квантовой яме, либо во второй (рис. 2), что приводит к соответствующему изменению проводимостей туннельносвя-занных каналов.

В соответствии с принципами УМТ [1], необходимым условием достижения задержки переключения ТСН меньшей, чем время пролета носителями каналов, является обеспечение практически неизменного суммарного числа подвижных носителей в квантовых ямах в процессе переключения структуры. Для выполнения данного условия при работе элемента в режиме большого сигнала необходимо на управляющие контакты ТСН подавать противофазные сигналы.

С целью формирования противофазных сигналов используется зеркальный принцип построения логических элементов. Например, на основе двух ТСН (п- и р-типа) реализуются два инвертора, работающие в противофазе (рис. 1а), а при реализации многовходовых логических вентилей И-НЕ в "зеркальных" элементах туннельносвязан-ные каналы соединяют по схеме ИЛИ-НЕ и наоборот (рис. 16).

СТРУКТУРА ТСН НА ОСНОВЕ ТУННЕЛЬНОСВЯЗАННЫХ КВАНТОВЫХ ЯМ

Принцип зеркальности требует для реализации логических функций вдвое больше каналов по сравнению, например, с КМОП-элементами. Использование в ТСН вертикальной интеграции обеспечивает примерно двукратное уменьшение площади, занимаемой элементами на кристалле, по сравнению с пленарным расположением ка-

налов. В результате площадь, занимаемая на кристалле логическими элементами с парафаз-ными входами/выходами, практически не увеличивается.

Следует отметить, что в некоторых случаях (например, в элементах статической памяти, рис. 3) "зеркальная" часть элемента может нести и самостоятельную функциональную нагрузку, что позволит дополнительно повысить эффективность использования площади кристалла СБИС.

Туннельносвязанные наноструктуры на основе гетеропереходов ваАв/АЮаАз с электронной и дырочной проводимостью показаны на рисунке 4.

Верхние управляющие переходы представляют собой переходы Шоттки, а нижние - соответственно р-п-переходы, выполненные с использованием скрытых п+ и р+-областей в эпитаксиальных слоях А^звао^Ав. Области ионного легирования разделены слоями широкозонного нелегированного А1А8 толщиной более 20 нм для предотвращения туннелирования носителей между ними. Легированные барьерные области п/р-А^Са^Ав отделены от квантовых ям ¿-А^Са^Ав спейсера-ми для ослабления рассеяния подвижных носителей в квантовых ямах на дальнодействующем ку-лоновском потенциале ионов примесей (рис. 4). Ширина квантовых ям составляет не менее 15 нм для уменьшения рассеяния подвижных носителей на границах гетеропереходов [3].

МОДЕЛИРОВАНИЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ НА ОСНОВЕ ТСН

Оценка статических характеристик логических элементов на основе ТСН производилась по результатам численного решения фундаментальной системы уравнений (ФСУ) полупроводника в диф-фузионно-дрейфовом приближении [4, 5] на двухмерных координатных сетках с использованием моделей подвижности носителей заряда, приведенных в [5, 6]. С целью обеспечения достаточной скорости сходимости при моделировании различных режимов работы элементов система уравнений решалась методом Ньютона [4].

При моделировании инвертора (рис. 1а) решение ФСУ осуществлялось отдельно для ТСН с электронной проводимостью и ТСН с дырочной проводимостью. В результате моделирования (рис. 5) для каждой ТСН были получены распределения потенциала (рис. 5а) и концентраций подвижных носителей (рис. 56) по координатам при различных напряжениях на внешних контактах, а после интегрирования плотности тока по площади контактов - семейства вольт-амперных характеристик (ВАХ, рис. 5в,г) для ТСН п-типа с длиной канала Ь = 200 нм (по оси у, рис. 5а,б), шири-

а

б

Рис. 4. Туннелыюсвязанные наноструктуры: а) с электронной проводимостью; б) с дырочной проводимостью

ной

Для дальнейшего прочтения статьи необходимо приобрести полный текст. Статьи высылаются в формате PDF на указанную при оплате почту. Время доставки составляет менее 10 минут. Стоимость одной статьи — 150 рублей.