МИКРОЭЛЕКТРОНИКА, 2015, том 44, № 5, с. 380-382

СХЕМОТЕХНИКА

УДК 621.382.322

МОДИФИЦИРОВАННАЯ КМДП СХЕМОТЕХНИКА "ДОМИНО"

© 2015 г. В. А. Лементуев

Учреждение Российской академии наук Институт проблем управления им. В.А. Трапезникова РАН, г. Москва E-mail: krikni@ipu.ru Поступила в редакцию 26.03.2015 г.

Предложена модифицированная КМДП схемотехника типа "Домино". На основе моделирования в системе SPICE тестовых и логических структур даны оценки временных параметров элементов схем.

DOI: 10.7868/S0544126915050075

1. ВВЕДЕНИЕ

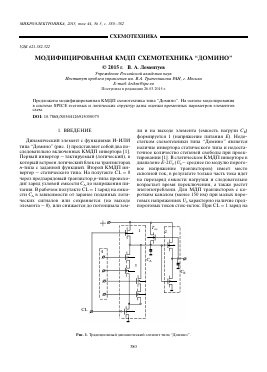

Динамический элемент с функциями И-ИЛИ типа "Домино" (рис. 1) представляет собой два последовательно включенных КМДП инвертора [1]. Первый инвертор — тактируемый (логический), в который встроен логический блок на транзисторах я-типа с заданной функцией. Второй КМДП инвертор — статического типа. На полутакте СЬ = 0 через предзарядовый транзистор ^-типа происходит заряд узловой емкости СА до напряжения питания. В рабочем полутакте СЬ = 1 заряд на емкости СА в зависимости от заранее поданных логических сигналов или сохраняется (на выходе элемента — 0), или снижается до потенциала зем-

ли и на выходе элемента (емкость нагрузи СВ) формируется 1 (напряжение питания Е). Недостатком схемотехники типа "Домино" является наличие инвертора статического типа и недостаточное количество степеней свободы при проектировании [1]. В статическом КМДП инверторе в диапазоне Е-2 и0 (и0 — среднее по модулю пороговое напряжение транзисторов) имеет место сквозной ток, в результате только часть тока идет на перезаряд емкости нагрузки и следовательно возрастает время переключения, а также растет энегопотреблени. Для МДП транзисторов с коротким каналом (менее 150 нм) при малых пороговых напряжениях и0 характерно наличие пред-пороговых токов сток-исток. При СЬ = 1 заряд на

Рис. 1. Традиционный динамический элемент типа "Домино"

МОДИФИЦИРОВАННАЯ КМДП СХЕМОТЕХНИКА "ДОМИНО

381

Рис. 2. Модифицированная КМДП-схемотехника типа "Домино"

емкости СА при реализации функции равной 0 может снизится на величину порогового напряжения транзистора р-типа и на выходе элемента возникает неопределенность. Для обесеченияя надежности функционирования при каскадном применении элемент типа "Домино" всегда дополняется транзистором обратной связи Тос р-типа [2].

2. МОДИФИЦИРОВАННЫЙ ЭЛЕМЕНТ "ДОМИНО"

Особенность схемы (см. рис. 2) — отсутствие тактируемых по СЬ МДП-транзисторов логического инвертора (1). Функцию тактируемой на-крузки, предзаряда и обратной связи (по традиционной схеме) выполняет траззистор Т 4 обратной связи р-типа. Тактовый транзистор Т1 и-типа и логические цепи типа И тактируются одновременно и непосредственно от СЬ сигналу. В цепь логического транзистора Т3 р-типа дополнительно включен транзистор Т 2 р-типа исключительно с целью ограничения потребляемой мощности на фронте сигнала СЬ = 1. Транзистор Т 2 является общим при каскадном включении логических элементов, когда элементы (при формировании 1) срабатывают поочередно, последовательно и его ток соответствует только одному элементу. При минимизиции ширины канала тактового транзистора Т1 и-типа и крутом фронте СЬ сигнала необходимость трензистора Т2 отпадает. Восста-

новление исходного состояния (СЬ = 1) на полутакте происходит за счет транзистора Т4 р-типа обратной связи, причем одновременно во всех каскадах логичесого устройства при закрытых логических цепях. Поэтому транзисторы Т1 и Т4 можно минимизировать по ширине каналов в зависимости глубины логики, т.е. времени полутакта логического устройства (СЬ = 1). Таким образом реализуется свобода выбора при задании параметров транзисторов Т1, Т 2 и Т4.

Время переключения Т0 из состояния логиче-кого 0 в 1 определяется временем ?10 разряда емкости СА через цепь логических транзисторов п-ти-па и временем ?01 заряда емкости нагрузи СВ через логический транзистор Т3 р-типа при закрытом тактовом транзисторе Т1. В зависимости от числа входов по И (и) и числа разветвлений по выходу (к) достаточно просто оптимизировать соотношения ширин Ж каналов логических транзисторов обоих типов и минимизировать суммарное время каскадного устройства Тж.

3. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ И ИХ ОБСУЖДЕНИЕ

Моделирование осуществлялось в системе PSPICE (версия 10.0,2004). Модели МДП (T55R) транзисторов — уровеня 7 (BSIM3 model version 3.1). Технологический процесс фирмы IBM-SCN013 (Lmin = 0.13 мкм, tox = 3.2 нм). Пороговые напряже-

МИКРОЭЛЕКТРОНИКА том 44 № 5 2015

382

ЛЕМЕНТУЕВ

ния транзисторов соответственно я- и ^-типов равны 0.42 и —0.44 В. Напряжение питания Усс = 2 В. Модель МДП-транзистора содержит полный набор емкостных составляющих всех электродов.

Тестовые схемы представляют собой 6 каскадов последовательно включенных инверторных структур 3 типов. Тип (1) — модифицированный элемент (согласно рис. 2) — логический транзистор = 3 мкм), логический транзистор Т3 ^-типа (Жр = 5 мкм). Тип (2) — тот же модифицированный логический элемент и статический инвертор = 3 мкм, Жр = 5 мкм). При этом тактовый транзистор Т1 (= 1 мкм), транзистор обратной

связи Т4 ^-типа (Жр = 1 мкм), а дополнительный транзистор Т2 для объективности сравнения отсутствует. Третий тип (3) — цепочка инверторов статического типа (= 3 мкм, Жр = 5 мкм). Тип (4) — модифицированный элемент с теми же параметрами (логические транзисторы по и = = 3 мкм). На двух пассивных входах логического элемента присутствуют сигналы логической 1 (напряжения питания Е). Считывание временного интервала (в пс) на уровне 0.5 амплитуды осуществлялось между соответствующими фронтами 3 и 4 каскадов для исключения влияния фронта тактового сигнала. Результаты моделирования приведены ниже.

Тип 1 ¿10 = 7.3 ¿01 = 7.7 Т0 = = 15

Тип 2 ¿10 = 10.6 ¿01 = 9.4 Т0 = 20

Тип 3 ¿10 = 12.6 ¿01 = 14.4 Т0 = 27

Тип 4 ¿10 = 15.4 ¿01 = 12.6 Т0 = 28

Прежде всего важно отметить роль одновременного тактирования логической части и тактового транзистора инвертирующего элемента по сравнению с инвертором статическго типа (тип 1 и тип 2 — аналога традиционного "Домино"). Задержка Т0 снижается в 1.3 раза как за счет уменьшения емкостной нагрузки СА, так и за счет отсутствия сквозного тока инвертора при формировании на выходе логической 1.

Сравнительный анализ обобщенных показателей по быстродействию показывает, что модернизированная схемотехника на уровне пары инверторов в 1.8 раза (тип 1 и тип 3) более эффективна, чем статическая КМДП логика.

Элемент 3И (тип 4) по быстродействию соответствует двухзвенной цепи статических КМДП инверторов (тип 3), но функционально намного полнее.

По затратам площиди кристалла модифицированная схемотехника — 3 транзистора на каскад, (кроме логических по И) более экономична, чем традиционная схемотехника "Домино" (5 транзисторов на каскад). При этом реализуется свобо-

да выбора при задании параметров транзисторов, не связанных с передачей логического сигнала (71, Т2 и Т4).

4. ЗАКЛЮЧЕНИЕ

Динамическая схемотехника типа "Домино" в настоящее время является базовым типом цифровой схемотехники. Для нее характеры отсутствие гонок тактовых сигналов и логических соревнований. Предложеная модифицированная схемотехника типа "Домино" в 1.3—1.8 раз более эффективна по быстродействию, позволяет минимизировать энергопотребление и требует миньших затрат площади кристалла.

СПИСОК ЛИТЕРАТУРЫ

1. Ватанабе М., Асада К., Кане К., Оцуки Т. Проектирование СБИС. М.: Мир. 1988, с. 90.

2. Chuang Y.C., Lu P., Anderccon C. SOI for Digital CMOS VLSI // Proceedings IEEE. 1998. V. 86. № 4. P. 689-718.

3. Лементуев В.А. Тактируемый логический элемент И-ИЛИ. Патент P^.(RU) 2368072, 2009.

МИКРОЭЛЕКТРОНИКА том 44

№ 5 2015

Для дальнейшего прочтения статьи необходимо приобрести полный текст. Статьи высылаются в формате PDF на указанную при оплате почту. Время доставки составляет менее 10 минут. Стоимость одной статьи — 150 рублей.